УДК 004.31

# РАЗРАБОТКА И ИССЛЕДОВАНИЕ МОДУЛЯ ПОДСИТЕМЫ ДИСПЕТЧЕРИЗАЦИИ ЗАДАЧ РЕКОНФИГУРИРУЕМОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ ДЛЯ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛА

### Мартенс-Атюшев Д.С., Мартышкин А.И.

Пензенский государственный технологический университет, Пенза, e-mail: Alexey314@yandex.ru

Сегодня, благодаря доступности микроэлектронных компонентов, возможно создание многопроцессорных и многоядерных систем разной мощности. Среди них, например, можно выделить реконфигурируемые вычислительные системы на основе программируемых логических интегральных схем. Целью статьи является изучение варианта архитектуры подсистемы планирования и назначения задач реконфигурируемых вычислительных систем для цифровой обработки сигналов. Для достижения этой цели использовались методы проектирования и построения вычислительных систем. Для всех математических расчетов применялись открытые сети массового обслуживания, которые хорошо описаны. В результате на созданном лабораторном стенде производилась отладка и тестирование разработанной вычислительной системы. Внутренние связи и функционал системы описывается при помощи языка VHDL. Предлагаемое устройство может использоваться в области образования, в медицине, в геоинформационных системах, в системах безопасности и др. В заключении представлены основные результаты и выводы по данной работе.

Ключевые слова: высокопроизводительная вычислительная система, программная реализация, аппаратная реализация, диспетчер задач, планировщик, реконфигурируемая система, математическая модель

## DEVELOPMENT AND RESEARCH THE MODULE OF TASK SCHEDULING SUBSYSTEM OF RECONFIGURABLE COMPUTATIONAL SYSTEM FOR DIGITAL SIGNAL PROCESSING

### Martens-Atushev D.S., Martyshkin A.I.

Penza State Technological University, Penza, e-mail: Alexey314@yandex.ru

Today, due to the availability of microelectronic components, it is possible to create multiprocessor and multicore systems of different capacities. Among them, for example, can be distinguished reconfigurable computing systems based on programmable logic integrated circuits. The purpose of the article is to study the architecture variant of the subsystem of planning and assigning tasks of reconfigurable computer systems for digital signal processing. To achieve this goal, methods of designing and building computer systems were used. For all mathematical calculations, open queuing networks were used, which are well described. As a result, the debugging and testing of the developed computer system was performed on the created laboratory bench. Internal communications and the functional of the system are described using the language VHDL. The proposed device can be used in the field of education, medicine, geoinformation systems, security systems, etc. In conclusion, the main results and conclusions on this work are presented.

Keywords: High-performance computing system, software implementation, hardware implementation, task manager, scheduler, reconfigurable system, mathematical model

Одной из основных проблем в высокопроизводительных вычислительных системах (ВС) является планирование и диспетчеризация задач. Потому обычно использующаяся программная реализация функций диспетчеризации способствует увеличению временных затрат на синхронизацию процессов, что отражается на работе всей системы в целом. Для разрешения данной ситуации существуют подходы в виде аппаратной реализации подсистемы планирования и диспетчеризации с единой очередью готовых к обслуживанию процессов и распределенной на каждый процессор (ЦП) [6].

Для обзора решения поставленной задачи, в данной работе рассмотрен диспетчер задач (ДЗ) с общей очередью. Представлено два вида моделирования, аналитическое в виде сети массового обслуживания

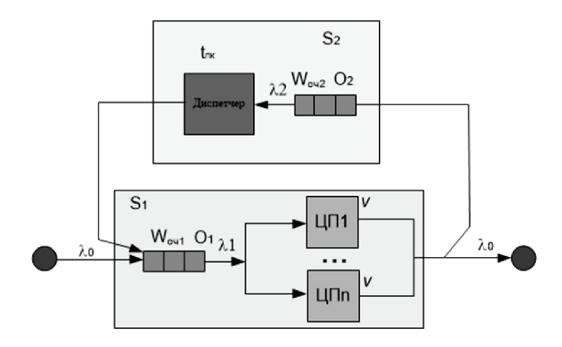

и имитационное, реализованное с помощью языка описания аппаратуры VHDL. Разработанное VHDL-описание ДЗ включено в проект по разработке реконфигурируемой вычислительной системы [1, 4]. Моделирование, основанное на системах массового обслуживания, позволяет получить емкую статистику по результатам временных характеристик. Модель (рис. 1) ДЗ с разделением во времени представляет собой сеть массового обслуживания, состоящую из обслуживающего многоканального узла (блок ЦП) и одноканального, которым является ДЗ. Задача, которая поступает из источника  $S_0$  с интенсивностью  $\lambda_0$ , назначается в любой ЦП. Для получения приблизительных результатов математического моделирования системы используется равновероятное назначение задач, это позволит обойти

Рис. 1. Исследуемая система с общим диспетчером

перегрузку системы, при простаивании некоторых ЦП. Так как очередь имеет ограниченное число мест, то при ее переполнении часть ЦП будут приостанавливаться, ожидая обслуживания. Следовательно, интенсивность потока задач очереди  $O_1$  будет равна  $\lambda_1 = \lambda_0 + \lambda_2$ . Очередь формирующаяся перед ДЗ не превышает число ожидающих ЦП, то есть, n-1 задача будет ожидать в очереди  $O_2$  пока предыдущая задача пребывает на обслуживании в ДЗ, тогда интенсивность  $O_2$  будет равным  $\lambda_2 = \lambda_1 - \lambda_0$ .

В рассматриваемой модели использована очередь типа *FIFO*, которая использует меньше системных ресурсов для формирования очереди задач, так же она проста в реализации. Но при выборе очереди типа *FIFO* увеличение загрузки системы влечет за собой увеличение среднего времени ожидания обслуживания. Математическое выражение для системы с общим ДЗ, основанное на рассмотренной СМО, а также полученное из исследований [5]

$$W = \frac{W_{ou1}}{P_{10}} + \frac{W_{ou2} \cdot P_{12}}{P_{10}} = \frac{W_{ou1} + W_{ou2} \cdot P_{12}}{P_{10}} . \tag{1}$$

Время отклика системы рассчитывается по выражению из [5]

$$U = \frac{W_{out} + v}{P_{10}} + \frac{P_{12} \cdot (W_{ou2} + t_{IIK})}{P_{10}} = \frac{W_{ou1} + v + P_{12} \cdot (W_{ou2} + t_{IIK})}{P_{10}}.$$

(2)

С развитием микроэлектронных технологий, стало возможным применение новых архитектурных решений для повышения производительности ВС, так же в последние годы все чаще можно наблюдать, как различные ВС строятся без применения традиционных ЦП, взамен которых применяют ПЛИС. Данное решение применяется и для аппаратной реализации ДЗ, входящего в состав реконфигурируемой вычислительной системы (РВС), представляющей собой устройство, состоящее из 4 реконфигурируемых ЦП реализованных на ПЛИС. Построение всей РВС на ПЛИС позволяет достаточно быстро перестраивать устройство под различные классы задач. Более подробное описание РВС было рассмотрено в [2, 3].

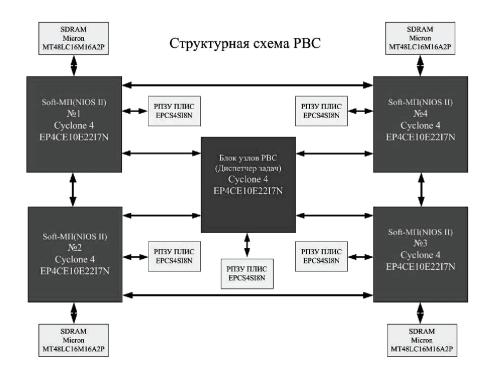

Представляемая PBC – это устройство, состоящее из 4 реконфигурируемых ЦП, реализованных аппаратно на ПЛИС (рис. 2).

одна ПЛИС выделена под блок связи узлов системы;

- 5 РПЗУ ПЛИС EPCS4SI8N фирмы Intel для хранения конфигурации каждой ПЛИС;

- 4 SDRAM MT48LC16M16A2 фирмы Micron, используемые как блоки ОЗУ.

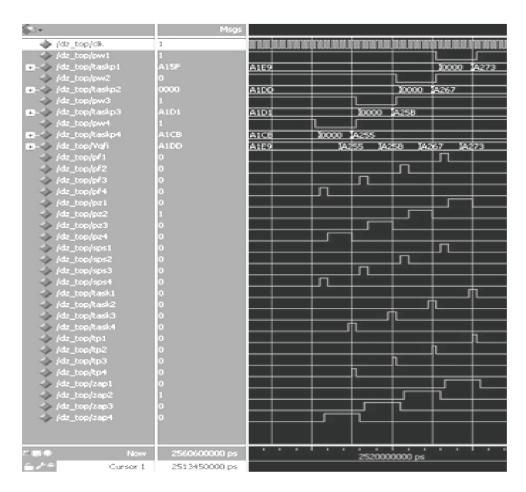

Моделирование разработанного проекта на языке VHDL, проводилось с помощью ПО ModelSim-Altera 10.0с. После компиляции была запущена симуляция проекта, где были получены временные диаграммы работы PBC (рис. 3). Диаграмма показывает, что идентификатор поступившей задачи под номером А255 передался на обработку в ЦП под номером 4 (taskp4), после чего ЦП выставил сигнал о том, что принял задачу на обработку (tp4). ЦП под номером 4 оказался занятым, поэтому следующий идентификатор задачи А25В принят на обработку в третий ЦП. Подобно четвертому

Рис. 2. Исследуемая реконфигурируемая вычислительная система

Разрабатываемая PBC состоит из следующих компонентов:

5 ПЛИС Cyclone 4 EP4CE10E22I7N фирмы Intel. 4 ПЛИС используются для реализации soft-микропроцессорных ядер Nios II,

ЦП, третий выставил сигнал (tp3) о том, что приступил к обслуживанию задачи. Такое назначение ЦП на обработку обусловлено схемой приоритетов от выполнения задач в системы, т.е. от четвертого ЦП к первому.

Рис. 3. Диаграммы работы системы в среде моделирования ModelSim-Altera 10.0c

В статье рассмотрена математическая модель ДЗ с единой очередью в составе РВС, представлена схема сети массового обслуживания, с помощью которой возможно рассмотреть аналитическое моделирование системы. Предложены математические выражения исследуемой модели. Разработано VHDL описание диспетчера задач, что позволяет оценить работу устройства в режиме реального времени.

Работа выполнена при финансовой поддержке РФФИ (Проект № 16–07–00012 A).

### Список литературы

1. Мартенс-Атюшев Д.С., Мартышкин А.И. Разработка и исследование реконфигурируемого вычислительного кластера для цифровой обработки сигнала // Современные информационные технологии. -2015. -№ 21. -ℂ. 190-195.

- 2. Мартенс-Атюшев Д.С., Мартышкин А.И. Разработка и исследование реконфигурируемой системы для цифровой обработки сигнала // Международный студенческий научный вестник. 2016. № 3–1. С. 86–88.

- 3. Мартенс-Атюшев Д.С., Мартышкин А.И. Разработка реконфигурируемой вычислительной системы для цифровой обработки сигнала // Технические науки — от теории к практике. — 2015. — № 52. — С. 50–58.

- 4. Мартенс-Атюшев Д.С., Мартышкин А.И. Реконфигурируемый вычислительный кластер для цифровой обработки сигнала // Современные методы и средства обработки пространственно-временных сигналов сборник статей XIII Всероссийской научно-технической конференции / Под редакцией И.И. Сальникова, 2015. С. 112–117.

- 5. Мартышкин А.И., Бикташев Р.А., Востоков Н.Г. Математическое моделирование диспетчеров задач для систем параллельной обработки на основе разомкнутых систем массового обслуживания // В мире научных открытий. -2013. -№ 6.1 (42). -C. 81–101.

- 6. Таненбаум Э., Бос X. Современные операционные системы. СПб.: Питер, 2015. 1120 с. ISBN: 978–5–496–01395–6.